# A look into the CXL device ecosystem and the evolution of CXL use cases

# Industry focal point

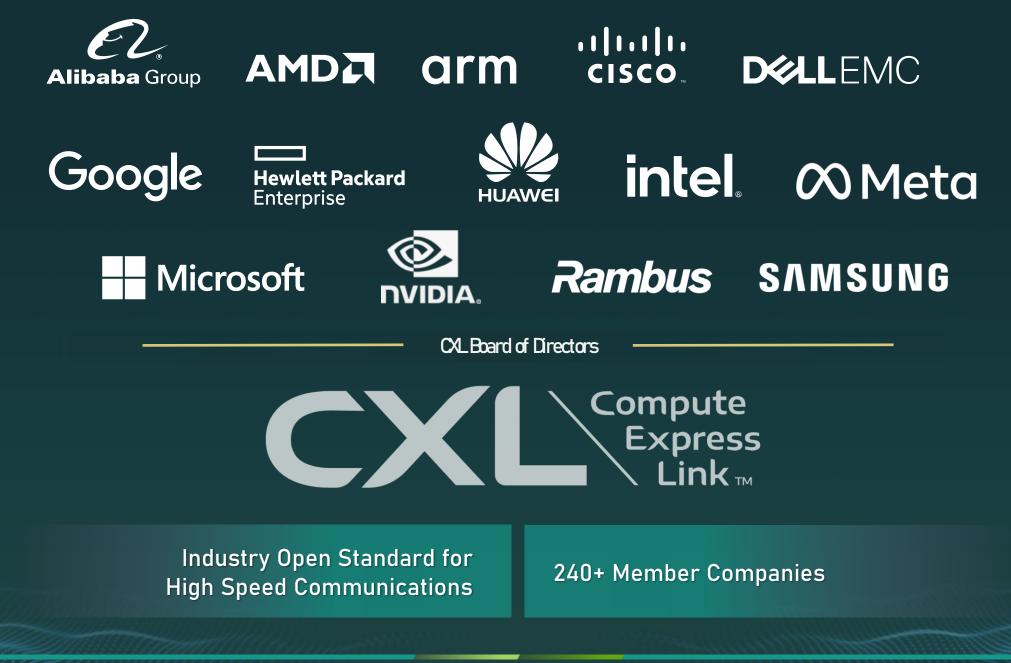

### CXL is emerging as the industry focal point for coherent IO

• CXL Consortium and OpenCAPI sign letter of intent to transfer OpenCAPI specification and assets to the CXL Consortium

August 1, 2022, Flash Memory Summit CXL Consortium and OpenCAPI Consortium Sign Letter of Intent to Transfer OpenCAPI Assets to CXL

In February 2022, CXL Consortium and Gen-Z Consortium signed agreement to transfer Gen-Z specification and assets to CXL Consortium

#### Industry Liaisons

# CXL is collaborating with industry organizations

## **CXL Delivers the Right Features & Architecture**

#### Challenges

Industry trends driving demand for faster data processing and next-gen data center performance

Increasing demand for heterogeneous computing and server disaggregation

Need for increased memory capacity and bandwidth

Lack of open industry standard to address next-gen interconnect challenges

CXL

An open industrysupported cachecoherent interconnect for processors, memory expansion and accelerators

#### Coherent Interface

Leverages PCIe<sup>™</sup> with 3 mix-andmatch protocols

#### Low Latency

.Cache and .Memory targeted at near CPU cache coherent latency

#### Asymmetric Complexity

Eases burdens of cache coherent interface designs

#### www.ComputeExpressLink.org

Compute Express Link™ and CXL™ are trademarks of the Compute Express Link Consortium.

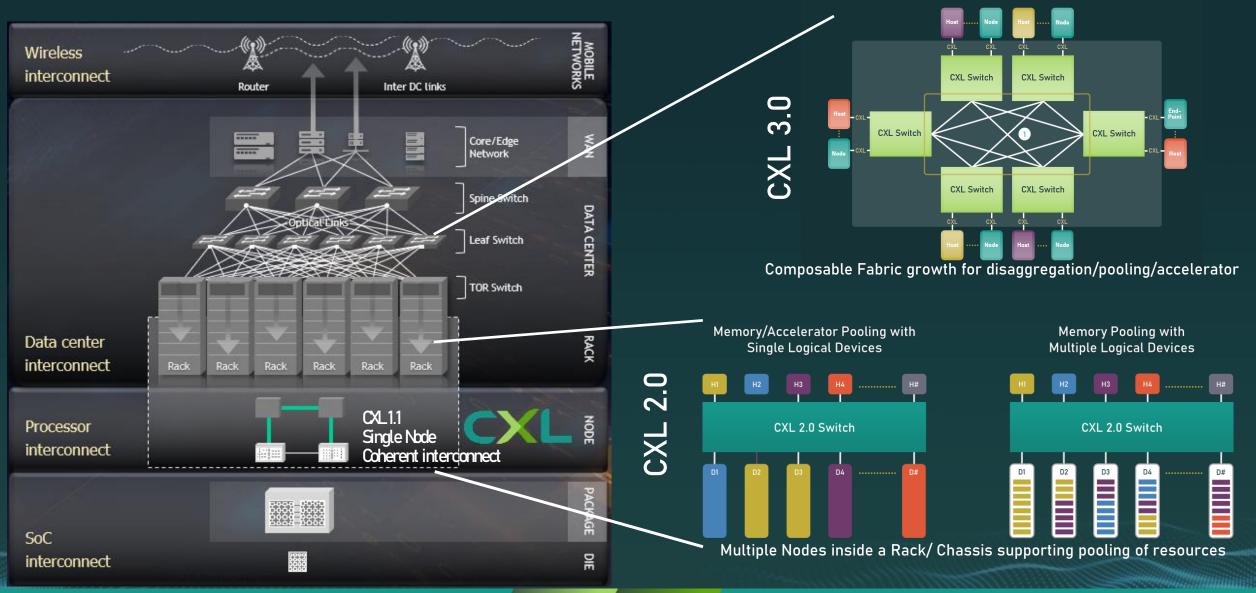

#### Data Center: Expanding Scope of CXL

### **CXL Spec Feature Summary**

| Features                                     | CXL 1.0 / 1.1 | CXL 2.0      | CXL 3.0      |

|----------------------------------------------|---------------|--------------|--------------|

| Release date                                 | 2019          | 2020         | August 2022  |

| Max link rate                                | 32GTs         | 32GTs        | 64GTs        |

| Flit 68 byte (up to 32 GTs)                  | $\checkmark$  | $\checkmark$ | $\checkmark$ |

| Flit 256 byte (up to 64 GTs)                 |               |              | $\checkmark$ |

| Type 1, Type 2 and Type 3 Devices            | $\checkmark$  | $\checkmark$ | $\checkmark$ |

| Memory Pooling w/ MLDs                       |               | $\checkmark$ | $\checkmark$ |

| Global Persistent Flush                      |               | $\checkmark$ | $\checkmark$ |

| CXL Integrity and Data Encryption (IDE)      |               | $\checkmark$ | $\checkmark$ |

| Switching (Single-level)                     |               | $\checkmark$ | $\checkmark$ |

| Switching (Multi-level)                      |               |              | $\checkmark$ |

| Direct memory access for peer-to-peer        |               |              | $\checkmark$ |

| Enhanced coherency (256 byte flit)           |               |              | $\checkmark$ |

| Memory sharing (256 byte flit)               |               |              | $\checkmark$ |

| Multiple Type 1/Type 2 devices per root port |               |              | $\checkmark$ |

| Fabric capabilities (256 byte flit)          |               |              | $\checkmark$ |

✓ Supported

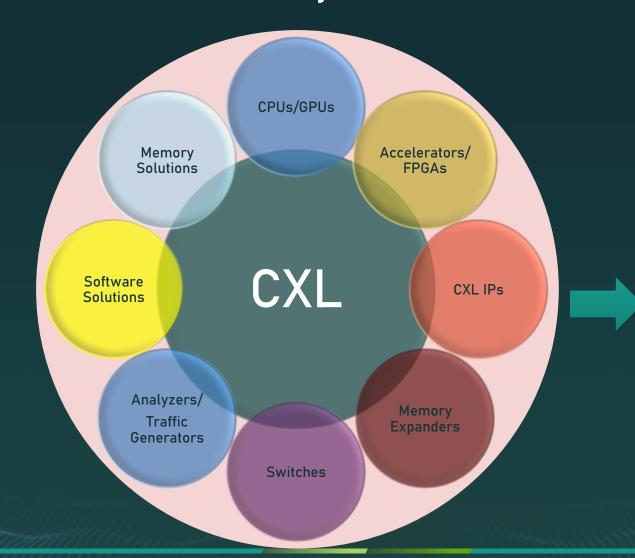

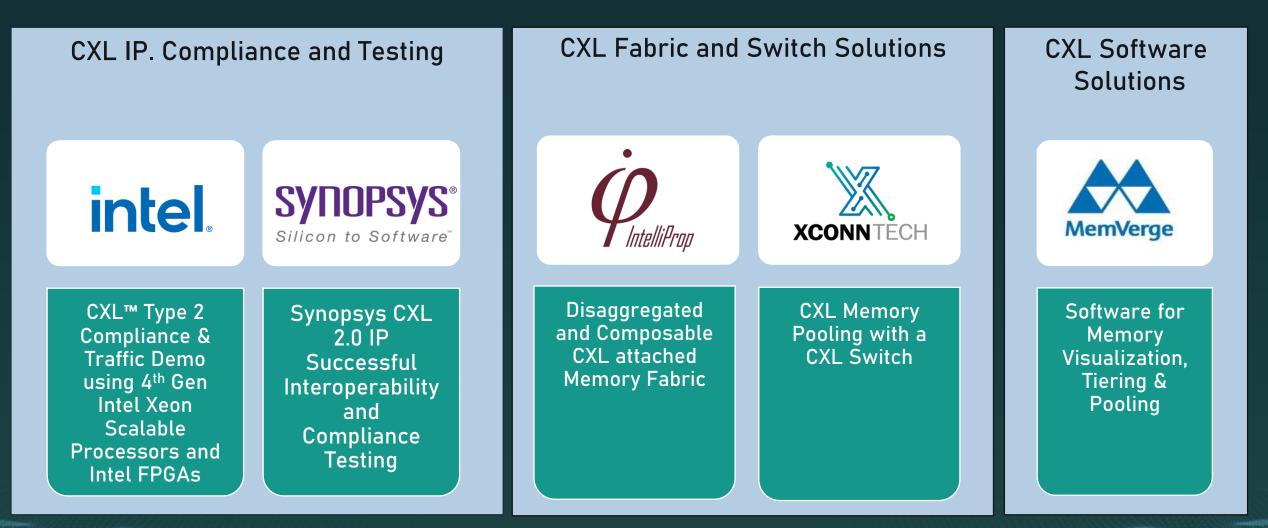

#### CXL Ecosystem & Demos and Evolving Use Cases

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### CXL Ecosystem Growth of CXL Ecosystem since its inception

- Ecosystem that meets the ever-increasing performance and scale requirements

- Fully backwards compatible

- Lowers overall system cost

•

• Comprehensive compliance and testing support

### **Evolving Use Cases**

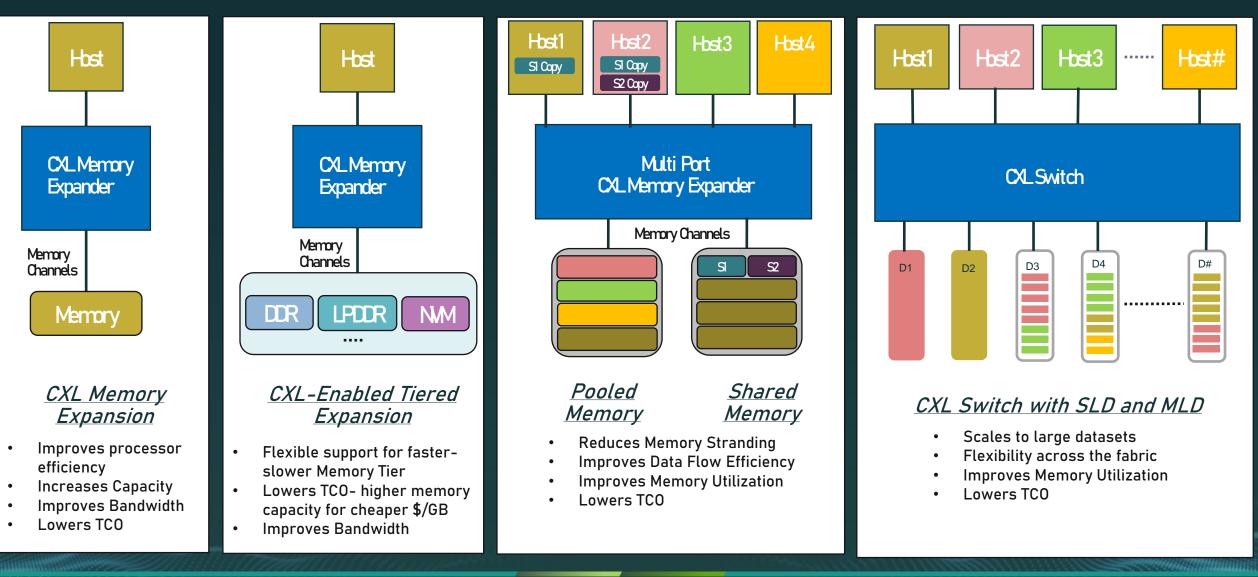

## Memory Pooling & Sharing

- Memory Pooling allows a host or multiple hosts to expand their memory capacity and bandwidth by using unique areas in a memory device with allocation of Memory segments tied to a unique host established at boot or a hot-swap event (i.e. memory segments accessed by a single host at runtime but can be migrated from host to host as needed).

- Memory Sharing allows multiple hosts to coherently share a common memory area in one or multiple memory devices. Multiple hosts can concurrently access and operate on that shared memory.

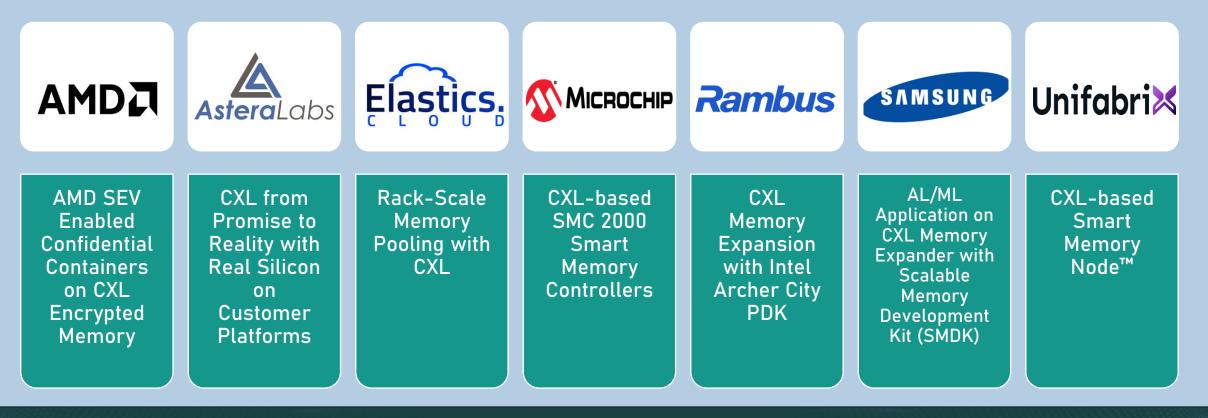

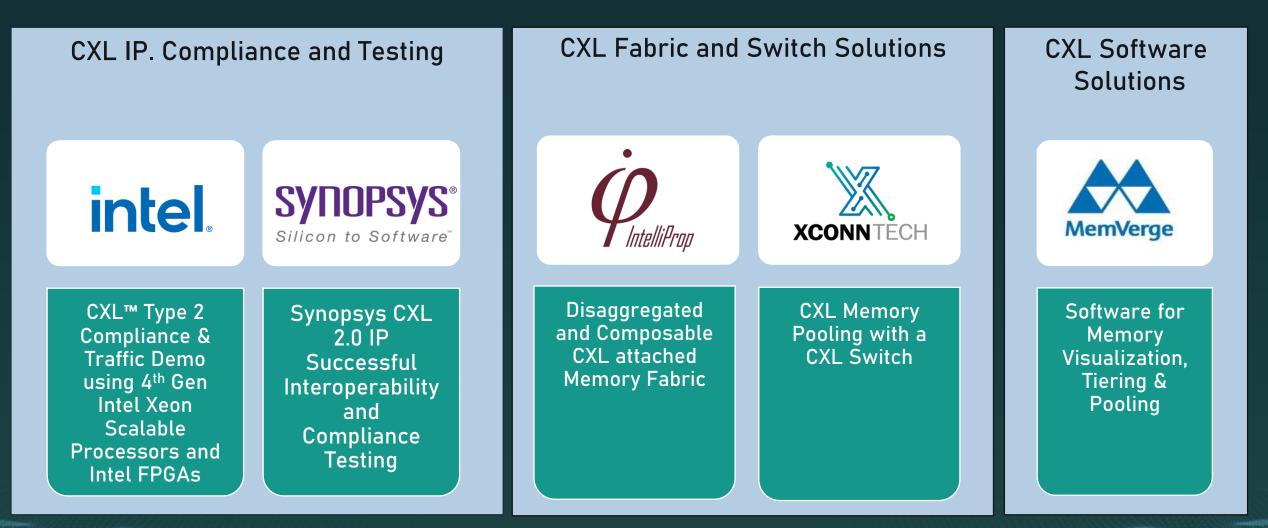

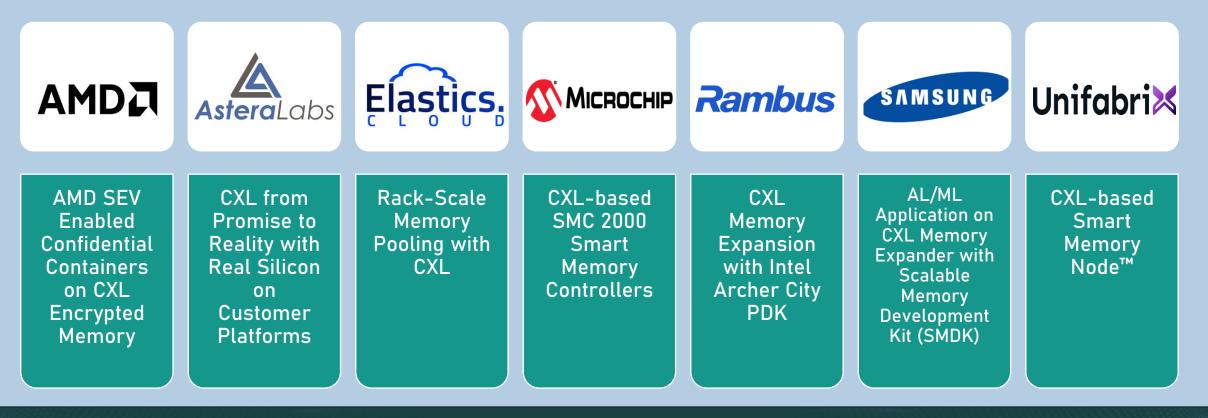

#### **CXL Memory Solutions**

### CXL at SC'22

- CXL is gaining momentum!

- SC'21: 5 live CXL demos

- SC'22: 12 live CXL demos

- CXL was recognized in the annual HPCWire Editors' Choice Award for Best HPC Interconnect Product or Technology

- View CXL technology demos: www.ComputeExpressLink.org/sc-22

Compute Express Link™ and CXL™ are trademarks of the Compute Express Link Consortium.

## Q&A Panel

······

#### **CXL Memory Solutions**

### Thank You

#### www.ComputeExpressLink.org

Compute Express Link™ and CXL™ are trademarks of the Compute Express Link Consortium.